- 您现在的位置:买卖IC网 > Sheet目录1223 > KSZ9692PB-EVAL (Micrel Inc)BOARD EVALUATION FOR KSZ9692PB

�� �

�

�

�Micrel,� Inc.�

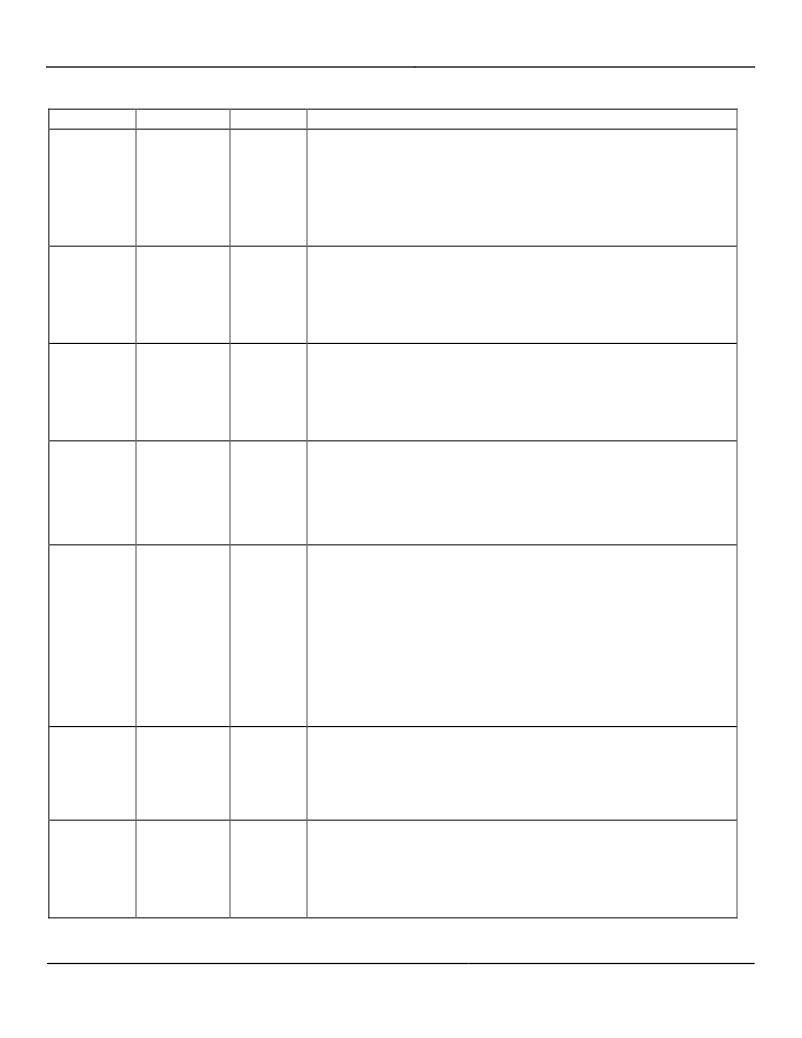

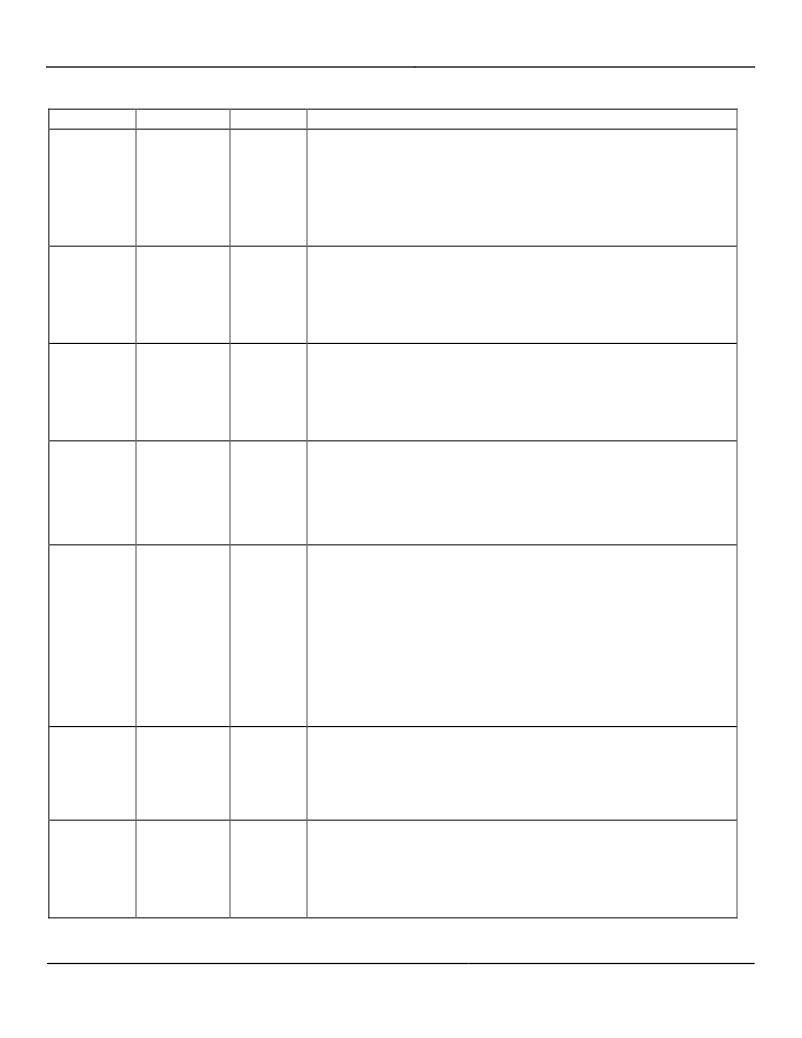

�Pin� Description:� Signal� Descriptions� by� Group� (Continued)�

�KSZ9692PB,� KSZ9692PB-S�

�Pin� Number�

�B1�

�Pin� Name�

�GNT1N�

�Pin� Type�

�O�

�Pin� Description�

�PCI� Bus� Grant� 1�

�Assert� Low.�

�In� Host� Bridge� Mode,� this� is� an� output� signal� from� the� internal� PCI� arbiter� to�

�grant� PCI� bus� access� to� the� master� driving� REQ1N.�

�In� Guest� Bridge� Mode,� this� is� an� output� signal� to� indicate� to� the� external� PCI�

�bus� arbiter� that� KSZ9692PB,� KSZ9692PB-S� is� requesting� access� to� the� PCI�

�bus.�

�D3�

�REQ3N�

�I�

�PCI� Bus� Request� 3�

�Assert� Low.�

�In� Host� Bridge� Mode,� this� is� an� input� signal� from� the� external� PCI� device� to�

�request� for� PCI� bus� access�

�In� Guest� Bridge� Mode,� this� is� unused.�

�E6�

�REQ2N�

�I�

�PCI� Bus� Request� 2�

�Assert� Low.�

�In� Host� Bridge� Mode,� this� is� an� input� signal� from� the� external� PCI� device� to�

�request� for� PCI� bus� access�

�In� Guest� Bridge� Mode,� this� is� unused.�

�C1�

�REQ1N�

�I�

�PCI� Bus� Request� 1�

�Assert� Low.�

�In� Host� Bridge� Mode,� this� is� an� input� signal� from� the� external� PCI� device� to�

�request� for� PCI� bus� access�

�In� Guest� Bridge� Mode,� this� signal� comes� from� the� external� arbiter� to� indicate�

�that� the� bus� is� granted� to� KSZ9692PB,� KSZ9692PB-S.�

�B3,� E7,� D6,�

�A2,� B4,� A3,�

�D7,� C5,� C6,�

�B5,� A4,� A5,�

�B6,� E8,� C7,�

�D8,� D10,� B10,�

�A11,� B11,�

�C11,� A12,�

�E11,� D11,�

�B12,� A13,�

�C12,� B13,�

�F12,� C13,�

�D12,� E12�

�A6,� A7,� E10,�

�C10�

�PAD[31..0]�

�CBEN[3..0]�

�I/O�

�I/O�

�32-bit� PCI� address� and� data� lines�

�Addresses� and� data� bits� are� multiplexed� on� the� same� pins.� During� the� first�

�clock� cycle� of� a� PCI� transaction,� the� PAD� bus� contains� the� first� clock� cycle� of� a�

�PCI� transaction,� the� PAD� bus� contains� the� physical� address.� During�

�subsequent� clock� cycles,� these� lines� contain� the� 32-bit� data� to� be� transferred.�

�Depending� on� the� type� of� the� transaction,� the� source� of� the� data� will� be� the�

�KSZ9692PB,� KSZ9692PB-S� if� it� initiates� a� PCI� write� transaction,� or� the� data�

�source� will� be� the� target� if� it� is� a� PCI� Read� transaction.� The� KSZ9692PB,�

�KSZ9692PB-S� bus� transaction� consists� of� an� address� phase� followed� by� one� or�

�more� data� phases.� The� KSZ9692PB,� KSZ9692PB-S� supports� both� Read� and�

�Write� burst� transactions.� In� case� of� a� Read� transaction,� a� special� data� turn�

�around� cycle� is� needed� between� the� address� phase� and� the� data� phase.�

�PCI� Commands� and� Byte� Enable,� asserted� Low.�

�The� PCI� command� and� byte� enable� signals� are� multiplexed� on� the� same� pins.�

�During� the� first� clock� cycle� of� a� PCI� transaction,� the� CBEN� bus� contains� the�

�command� for� the� transaction.� The� PCI� transaction� consists� of� the� address�

�phases� and� one� or� more� data� phases.� During� the� data� phases� of� the�

�transaction,� the� bus� carries� the� byte� enable� for� the� current� data� phases.�

�C8�

�PAR�

�I/O�

�Parity�

�PCI� Bus� parity� is� even� across� PAD[31:0]� and� CBEN[3:0].�

�The� KSZ9692PB,� KSZ9692PB-S� generates� PAR� during� the� address� phase� and�

�write� data� phases� as� a� bus� master,� and� during� read� data� phases� as� a� target.� It�

�checks� for� correct� PAR� during� read� data� phase� as� a� bus� master,� during� every�

�address� phase� as� a� bus� slave,� and� during� write� data� phases� as� a� target.�

�May� 2011�

�18�

�M9999-051111-4.0�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

L17-RR-D1-F-01-100

CONN SOCKET 20-24AWG CRIMP GOLD

L171370

D-SUB BACKSHELL BLACK PLAS 9POS

L17529

D-SUB ASSY SPRING LATCH

L17D204182TX

SCREWLOCK W/NUT/WASH 1=10 SETS

L17D204182X

CONN ACCESSORY SCREW LOCK ASSY

L17D20419EX

D-SUB ASSY SCREW LOCK ASSY 10PCS

L17D20419X

CONN D-SUB ACCESSORY SCREW LOCK

L17D4K63110

D-SUB 9POS FEMALE DUST COVER

相关代理商/技术参数

KSZ9692PBI

功能描述:网络控制器与处理器 IC Integrated Gigabit Ethernet and Communication Controller with IPSec (I-temp)

RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

KSZ9692PB-PTP-EVAL

制造商:Micrel Inc 功能描述:Eval Board for KSZ9692 Integrated Gigabit Networking /Communications Controller

KSZ9692XPB

功能描述:网络控制器与处理器 IC Integrated gigabit Ethernet and USB Controller, Lead Free

RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray

KT 10

制造商:Icotek 功能描述:Bulk

KT 1009

制造商:knitter-switch 功能描述:

KT 11

制造商:Icotek 功能描述:Bulk

KT 1117

制造商:knitter-switch 功能描述:

KT 12

制造商:Icotek 功能描述:Bulk 制造商:Weidmuller 功能描述:Bulk